大家好,我目前任職於某家SSD韌體,主要是負責NVMe Front-end的部分,Front-end主要

負責PCIe和NVMe protocol的firmware porting,所以必須study這兩份spec。由於spec

的內容過於龐大,所以我習慣會用網誌做筆記,一方便怕自己忘記,一方面也可以在遇到

問題的時候快速查詢,當然我所寫的都是我對於spec的理解,所以希望有這方面的專家,

可以討論不同的見解,也歡迎大家討論與指教。

PCIE:

■原理PCI Express - LTSSM Equalization狀態機推演

由於PCIe通道傳輸的特性,會有所謂的碼間干擾(Inter-Symbol Interference,ISI),而

導致資料無法被辨識,且隨著PCIe頻率越來越高,這個問題會更加明顯,因此必須透過

Equalizer來調整彼此間的訊號,得到比較好的眼圖,搭建起溝通的橋樑,此篇為EQ

LTSSM的推演。

https://reurl.cc/VjGMzb

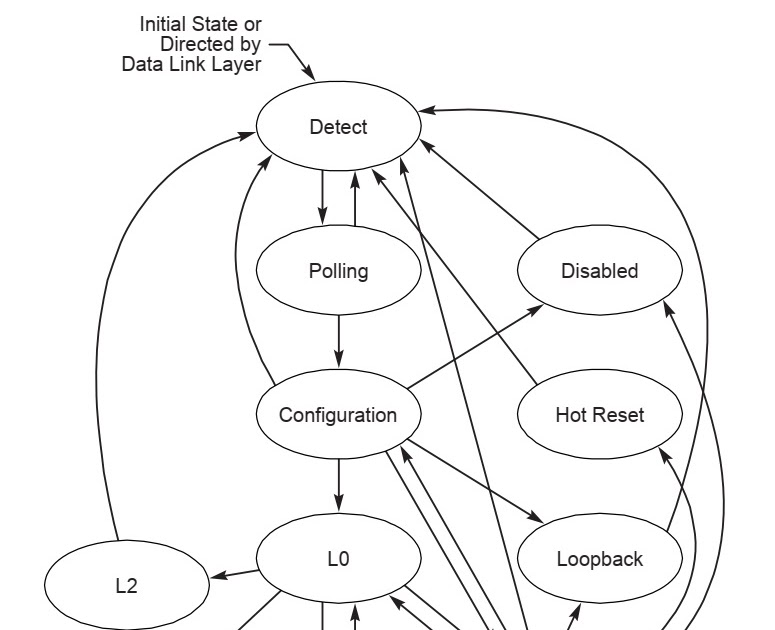

■原理PCI Express - LTSSM 狀態機推演 "Detect -> Polling -> Configuration ->

L0"

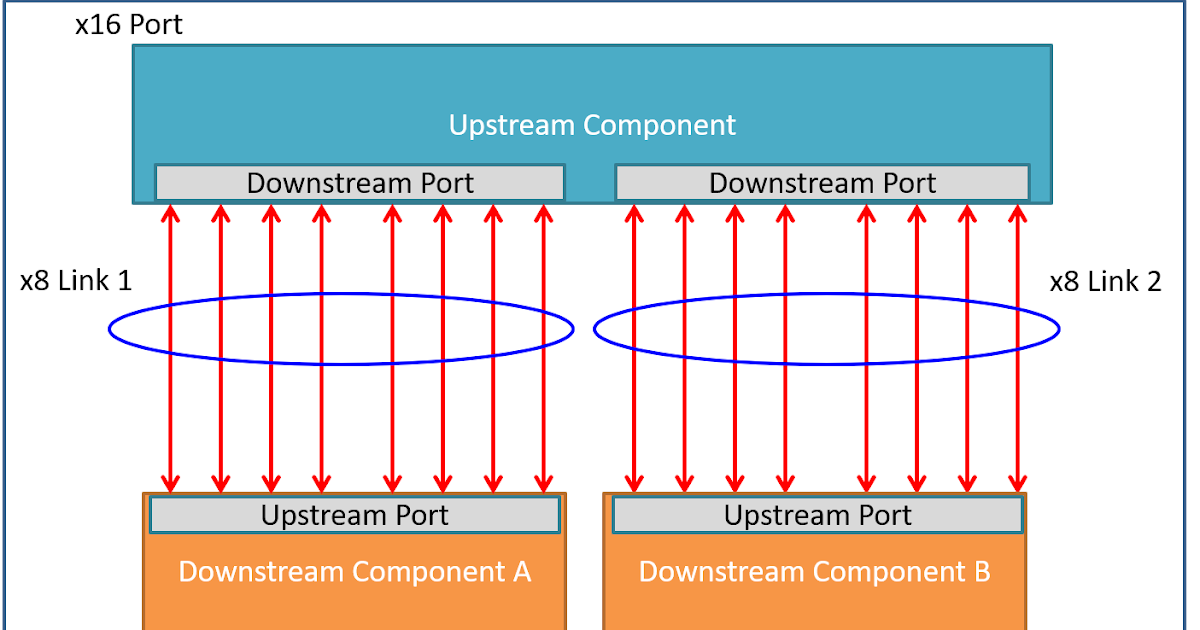

PCIe為point-to-point interconnects(點對點的連接),所以就算系統上由多層PCIe bus

所構成,每個component只要負責與他對面的component之間的link negotiation就可以了

,這篇文章主要會推演兩個端點之間的LTSSM是如何從Detect state演進到L0。

https://reurl.cc/akpd4D

■簡介PCI Express: Link Training and Status State Machine( LTSSM 狀態機 )

由於工作上很容易會遇到PCIe Link上的問題或者我們需要驗證LTSSM state transition

有沒有符合預期 ,常常需要透過Protocol Analyzer錄製PCIe Trace來進一步分析。此篇

主要會介紹Traning Sequence,和各個LTSSM state主要目的為何。

https://reurl.cc/9Od37x

■原理PCI Express: Advanced Error Reporting(AER)

Advanced Error Report(簡稱AER)為PCIe 較為強健的錯誤回報機制,在PCI Express?

Base Specification Revision 3.0 的6.2節"Error Signaling and Logging"章節有詳細

的介紹整個AER的logging與repoting機制,由於工作上常常遇到Linux Kernel log中,出

現AER error訊息,所以又把spec拿出來翻一翻,藉此寫一篇關於AER的機制,方便以後查

詢。

https://reurl.cc/veyva1

NVME:

■原理NVM Express - NVMe Submission Queue & Completion Queue (SQ & CQ)

NVMe最基本的communicate架構主要是建立在Submission Queue和Completion Queue,

Host Software透過Submission Queue來提交command讓NVMe Controller執行,

Controller會透過Completion Queue來回報command執行狀況為何。此篇主要介紹NVMe基

本架構。

https://reurl.cc/bkZYVd

--